## **Retrocomputing with Clash**

Haskell for FPGA Hardware Design

## Gergő Érdi

# Retrocomputing with Clash

Haskell for FPGA Hardware Design

GERGŐ ÉRDI

https://unsafePerform.IO/retroclash/

#### Retrocomputing with Clash: Haskell for FPGA Hardware Design

Copyright ©2021 Gergő Érdi

All rights reserved. No part of this book may be reproduced, distributed, or transmitted in any form or by any means, including photocopying, recording, or other electronic or mechanical methods, without the prior written permisison of the copyright owner, except for the use of quotations in a book review and certain other noncommercial uses permitted by copyright law.

First edition, 2021.

Cover by Jutka Sallai

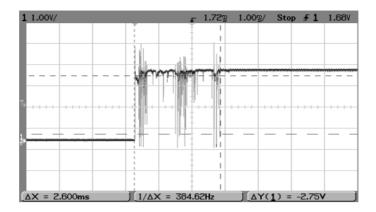

Bouncy pushbutton scope screenshot from https://commons.wikimedia.org/wiki/File: Bouncy\_Switch.png licensed under the terms of the Creative Commons CC0 1.0 Universal Public Domain Dedication ©

https://unsafePerform.IO/retroclash/

### Contents

| Introduction |        |                                                          | 1  |

|--------------|--------|----------------------------------------------------------|----|

| 1            | Into t | he world of FPGAs                                        | 5  |

|              | 1.1    | Computers everywhere                                     | 5  |

|              | 1.2    | Field-programmable Gate Arrays                           | 8  |

|              | 1.3    | Retrocomputing                                           | 15 |

|              | 1.4    | Haskell meets Hardware                                   | 16 |

| 2            | Hello  | o, Clash!                                                | 19 |

|              | 2.1    | Bit                                                      | 19 |

|              | 2.2    | Signal                                                   | 20 |

|              | 2.3    | Our first circuit                                        | 20 |

|              | 2.4    | Summary                                                  | 25 |

| 3            | Comb   | pinational Circuits are Applicative Functors             | 27 |

|              | 3.1    | Signal is an applicative functor                         | 27 |

|              | 3.2    | BitVectors and Vectors                                   | 29 |

|              | 3.3    | Controlling many LEDs                                    | 30 |

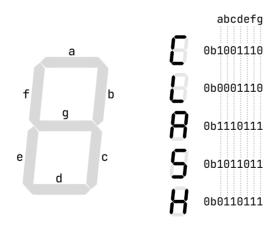

|              | 3.4    | Seven-segment display                                    | 32 |

|              | 3.5    | Summary                                                  | 38 |

| 4            | State, | Sequencing and Clocks: The Register Transfer-Level Model | 39 |

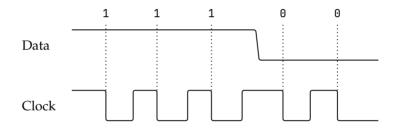

|              | 4.1    | Clocks and registers                                     | 40 |

|              | 4.2    | The RTL model: register and delayed feedback             | 42 |

|              | 4.3    | Finally blinkenlights!                                   | 46 |

|              | 4.4    | Passing around Clock, Reset and Enable lines implicitly  | 51 |

|              | 4.5    | Multiple clocks                                          | 54 |

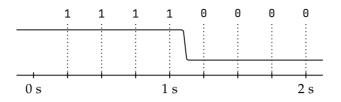

|              | 4.6    | Pushbutton-toggled LED                                   | 55 |

|              | 4.7    | Summary                                                  | 60 |

|   | Time                                                                                                                                                                     | -domain Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                                                    |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|   | 5.1                                                                                                                                                                      | Does this have anything to do with mux?                                                                                                                                                                                                                                                                                                                                                                                   | 63                                                                                                    |

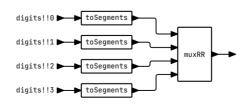

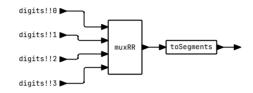

|   | 5.2                                                                                                                                                                      | Seven-segment displays, revisited                                                                                                                                                                                                                                                                                                                                                                                         | 64                                                                                                    |

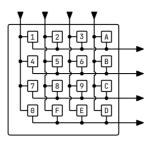

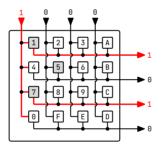

|   | 5.3                                                                                                                                                                      | Keyboard matrix sweeping                                                                                                                                                                                                                                                                                                                                                                                                  | 69                                                                                                    |

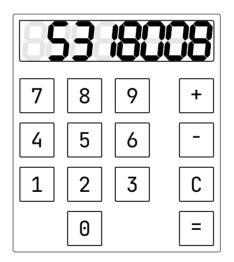

|   | 5.4                                                                                                                                                                      | Showing keypad input on a seven-segment output                                                                                                                                                                                                                                                                                                                                                                            | 74                                                                                                    |

|   | 5.5                                                                                                                                                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                   | 78                                                                                                    |

| 6 | Proje                                                                                                                                                                    | ct: Pocket Calculator                                                                                                                                                                                                                                                                                                                                                                                                     | 79                                                                                                    |

|   | 6.1                                                                                                                                                                      | A Minimal Viable Calculator                                                                                                                                                                                                                                                                                                                                                                                               | 79                                                                                                    |

|   | 6.2                                                                                                                                                                      | Binary Coded Decimal arithmetic                                                                                                                                                                                                                                                                                                                                                                                           | 81                                                                                                    |

|   | 6.3                                                                                                                                                                      | State and state transitions                                                                                                                                                                                                                                                                                                                                                                                               | 85                                                                                                    |

|   | 6.4                                                                                                                                                                      | An interactive software implementation                                                                                                                                                                                                                                                                                                                                                                                    | 89                                                                                                    |

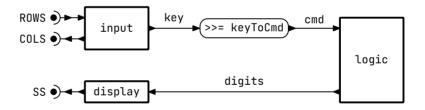

|   | 6.5                                                                                                                                                                      | Hooking it up to hardware peripherals                                                                                                                                                                                                                                                                                                                                                                                     | 91                                                                                                    |

|   | 6.6                                                                                                                                                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                   | 95                                                                                                    |

| 7 | Vide                                                                                                                                                                     | o Output Using VGA                                                                                                                                                                                                                                                                                                                                                                                                        | 97                                                                                                    |

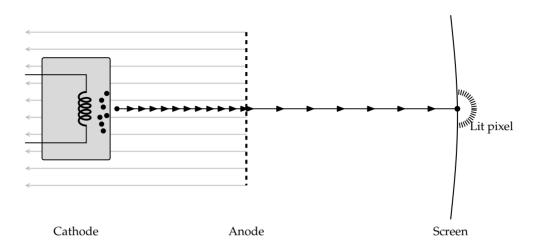

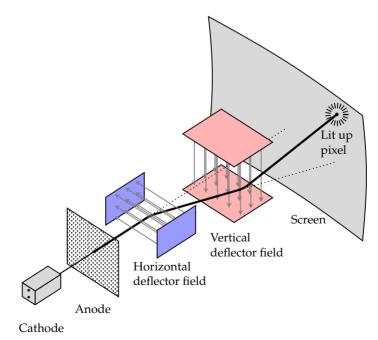

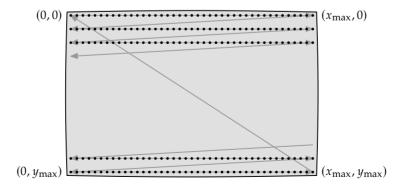

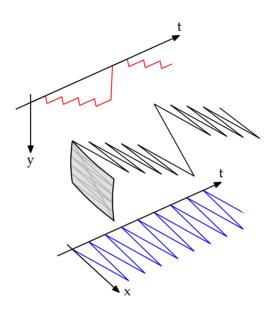

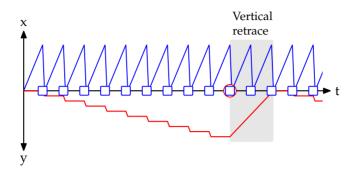

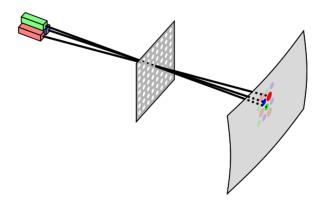

|   | 7.1                                                                                                                                                                      | Basic operation of a CRT display                                                                                                                                                                                                                                                                                                                                                                                          | 97                                                                                                    |

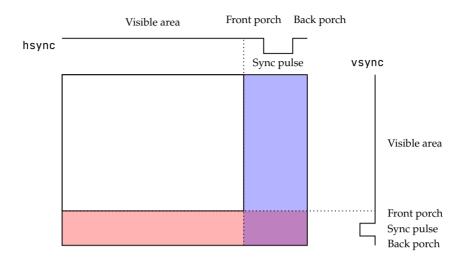

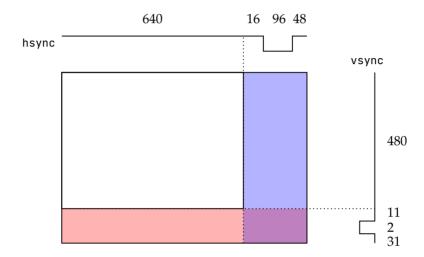

|   | 7.2                                                                                                                                                                      | Video Graphics Array                                                                                                                                                                                                                                                                                                                                                                                                      | 101                                                                                                   |

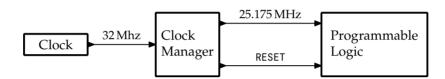

|   | 7.3                                                                                                                                                                      | VGA from Clash                                                                                                                                                                                                                                                                                                                                                                                                            | 106                                                                                                   |

|   | 7.4                                                                                                                                                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                   | 114                                                                                                   |

| 8 | Gene                                                                                                                                                                     | erative Graphics                                                                                                                                                                                                                                                                                                                                                                                                          | 117                                                                                                   |

|   |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

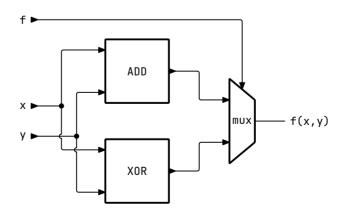

|   | 8.1                                                                                                                                                                      | Combinational patterns                                                                                                                                                                                                                                                                                                                                                                                                    | 117                                                                                                   |

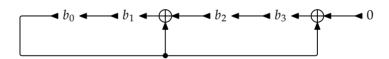

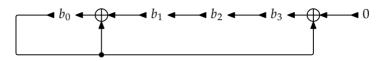

|   | 8.1<br>8.2                                                                                                                                                               | Stateful pattern generators                                                                                                                                                                                                                                                                                                                                                                                               | 118                                                                                                   |

|   |                                                                                                                                                                          | *                                                                                                                                                                                                                                                                                                                                                                                                                         | 118                                                                                                   |

|   | 8.2                                                                                                                                                                      | Stateful pattern generators                                                                                                                                                                                                                                                                                                                                                                                               | 118<br>120                                                                                            |

|   | 8.2<br>8.3                                                                                                                                                               | Stateful pattern generators    Animation                                                                                                                                                                                                                                                                                                                                                                                  | 118<br>120<br>124                                                                                     |

|   | 8.2<br>8.3<br>8.4                                                                                                                                                        | Stateful pattern generators       Animation         Animation       Coordinate transformations                                                                                                                                                                                                                                                                                                                            | 118<br>120<br>124<br>130                                                                              |

|   | 8.2<br>8.3<br>8.4<br>8.5                                                                                                                                                 | Stateful pattern generators       Animation         Animation       Coordinate transformations         Animation, differently       Animation                                                                                                                                                                                                                                                                             | 118<br>120<br>124<br>130<br>135                                                                       |

| 9 | 8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7                                                                                                                                   | Stateful pattern generators       Animation         Animation       Coordinate transformations         Animation, differently       Animation         High-level simulation with SDL2       Summary         Summary       Summary                                                                                                                                                                                         | <ol> <li>118</li> <li>120</li> <li>124</li> <li>130</li> <li>135</li> <li>143</li> <li>145</li> </ol> |

| 9 | 8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7                                                                                                                                   | Stateful pattern generators                                                                                                                                                                                                                                                                                                                                                                                               | <ol> <li>118</li> <li>120</li> <li>124</li> <li>130</li> <li>135</li> <li>143</li> <li>145</li> </ol> |

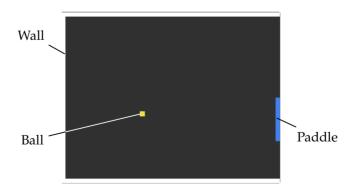

| 9 | 8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>Proje                                                                                                                          | Stateful pattern generators       Animation         Animation       Coordinate transformations         Animation, differently       Animation         High-level simulation with SDL2       Summary         Summary       Summary                                                                                                                                                                                         | <ol> <li>118</li> <li>120</li> <li>124</li> <li>130</li> <li>135</li> <li>143</li> <li>145</li> </ol> |

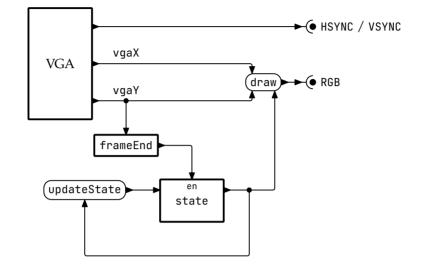

| 9 | 8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br><b>Proje</b><br>9.1                                                                                                            | Stateful pattern generators       Animation         Animation       Coordinate transformations         Animation, differently       Animation, differently         High-level simulation with SDL2       Summary         Summary       Summary         ct: Pong         What is Pong?       Summary                                                                                                                       | 118<br>120<br>124<br>130<br>135<br>143<br><b>145</b><br>145<br>146                                    |

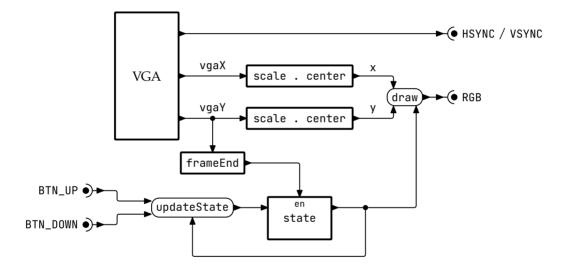

| 9 | 8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br><b>Proje</b><br>9.1<br>9.2                                                                                                     | Stateful pattern generators       Animation         Animation       Coordinate transformations         Animation, differently       Animation, differently         High-level simulation with SDL2       Summary         Summary       Summary         ct: Pong         What is Pong?       Summary         Top-level design       Summary                                                                                | 118<br>120<br>124<br>130<br>135<br>143<br><b>145</b><br>145<br>146                                    |

| 9 | 8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br><b>Proje</b><br>9.1<br>9.2<br>9.3                                                                                              | Stateful pattern generators       Animation         Animation       Coordinate transformations         Animation, differently       Animation, differently         High-level simulation with SDL2       Summary         Summary       Summary         ct: Pong         What is Pong?       Summary         Top-level design       Summary         What is our state?       Summary                                       | 118<br>120<br>124<br>130<br>135<br>143<br><b>145</b><br>145<br>146<br>148<br>153                      |

| - | <ul> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>8.6</li> <li>8.7</li> <li>Proje</li> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> </ul> | Stateful pattern generators       Animation         Animation       Coordinate transformations         Animation, differently       Animation, differently         High-level simulation with SDL2       Summary         Summary       Summary         ct: Pong         What is Pong?       Summary         Top-level design       Summary         What is our state?       Summary                                       | 118<br>120<br>124<br>130<br>135<br>143<br><b>145</b><br>145<br>146<br>148<br>153                      |

| - | <ul> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>8.6</li> <li>8.7</li> <li>Proje</li> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> </ul> | Stateful pattern generators         Animation         Coordinate transformations         Animation, differently         High-level simulation with SDL2         Summary         ct: Pong         What is Pong?         Top-level design         What is our state?         Drawing         Summary                                                                                                                        | 118<br>120<br>124<br>130<br>135<br>143<br><b>145</b><br>145<br>146<br>148<br>153<br>154               |

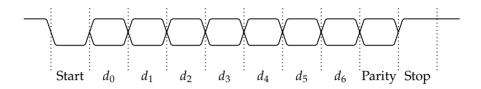

| - | 8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br><b>Proje</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br><b>Asym</b>                                                                 | Stateful pattern generators       Animation         Animation       Coordinate transformations         Animation, differently       Animation, differently         High-level simulation with SDL2       Summary         Summary       Summary         ct: Pong       Vhat is Pong?         What is Pong?       Drawing         Drawing       Summary         Summary       Summary         Chronous Serial Communication | 118<br>120<br>124<br>130<br>135<br>143<br>145<br>145<br>146<br>148<br>153<br>154<br><b>155</b>        |

|    | 10.4  | Serial Receiver                         | 165 |

|----|-------|-----------------------------------------|-----|

|    | 10.5  | Applications                            | 168 |

|    | 10.6  | Summary                                 | 172 |

| 11 | Progr | rammable Machines                       | 173 |

|    | 11.1  | RAM machines                            | 173 |

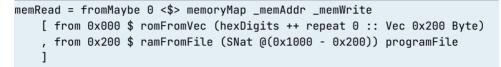

|    | 11.2  | Memory                                  | 175 |

|    | 11.3  | СРИ                                     | 181 |

|    | 11.4  | Summary                                 | 186 |

| 12 | Brain | fuck                                    | 187 |

|    | 12.1  | Why Brainfuck                           | 187 |

|    | 12.2  | Brainfuck as a programming language     |     |

|    | 12.3  | Brainfuck as byte code                  |     |

|    | 12.4  | Brainfuck with external memory          |     |

|    | 12.5  | A complete Brainfuck computer           |     |

|    | 12.6  | Brainfuck as machine code               |     |

|    | 12.7  | High-level simulation of the CPU        |     |

|    | 12.8  | The logic board                         |     |

|    | 12.9  | Low-level simulation of the logic board |     |

|    | 12.10 | Top-level circuit and peripherals       |     |

|    | 12.11 | Summary                                 |     |

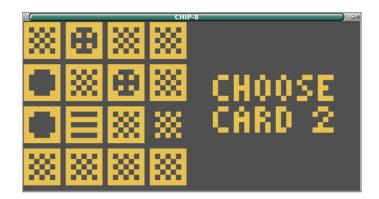

| 13 | CHIP  | -8                                      | 237 |

|    | 13.1  | History                                 |     |

|    | 13.2  | The CHIP-8 computer                     |     |

|    | 13.3  | Instruction set                         |     |

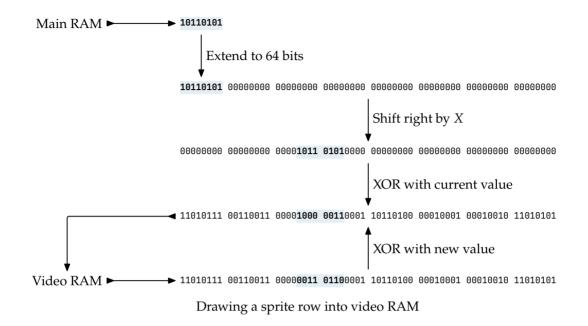

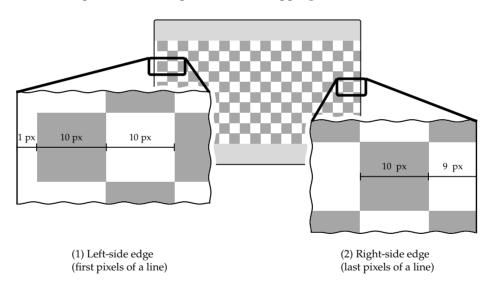

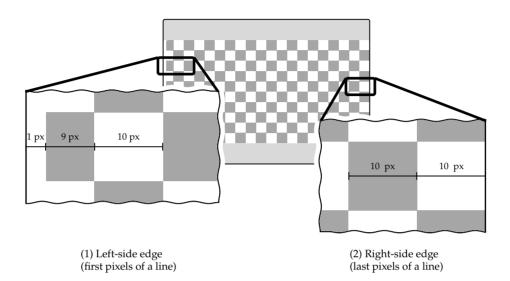

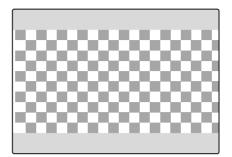

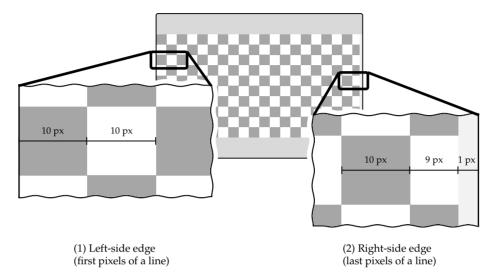

|    | 13.4  | Video                                   |     |

|    | 13.5  | СРИ                                     |     |

|    | 13.6  | Simulation, take 1                      |     |

|    | 13.7  | The complete machine                    |     |

|    | 13.8  | Simulation, take 2                      |     |

|    | 13.9  | Memory contention                       |     |

|    | 13.10 | Summary                                 |     |

| 14 | Addre | ess decoding and memory maps            | 303 |

|    | 14.1  | Room for improvement                    |     |

|    | 14.2  | A whirlwind intro to Template Haskell   |     |

|    | 14.3  | A memory map DSL                        |     |

|    | 14.4  | Backpane connections                    |     |

|    | 14.5  | Access contention                       |     |

|                   | 14.6  | Summary                                       | 329               |

|-------------------|-------|-----------------------------------------------|-------------------|

| 15 Intel 8080 331 |       |                                               |                   |

|                   | 15.1  |                                               | 331               |

|                   | 15.2  | 5                                             | 331               |

|                   | 15.3  |                                               | 333               |

|                   | 15.4  | Instruction set architecture                  | 338               |

|                   | 15.5  |                                               | 344               |

|                   | 15.6  | Microcoded implementation                     | 349               |

|                   | 15.7  | -                                             | 357               |

|                   | 15.8  | A direct software implementation              | 376               |

|                   | 15.9  | The complete CPU                              |                   |

|                   | 15.10 | Summary                                       |                   |

| 10                | Ducia |                                               | 401               |

| 10                | 16.1  | <b>t: TinyBASIC</b> What is Tiny BASIC?       | <b>401</b><br>401 |

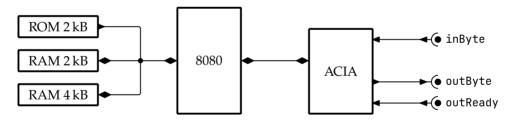

|                   | 16.1  | Asynchronous Communications Interface Adapter | 401               |

|                   | 16.2  | The core logic board                          | 402               |

|                   | 16.4  | Version 1: serial I/O                         | 404               |

|                   | 16.5  | PS/2 keyboard interface                       | 410               |

|                   | 16.6  | Textual video                                 | 417               |

|                   | 16.7  | Screen editing                                |                   |

|                   | 16.8  | Version 2: Keyboard and video                 | 427               |

|                   | 16.9  | Summary                                       | 428               |

|                   | _     |                                               |                   |

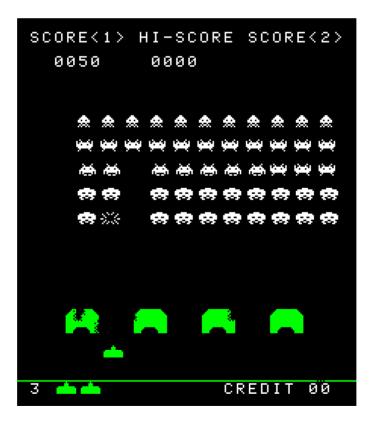

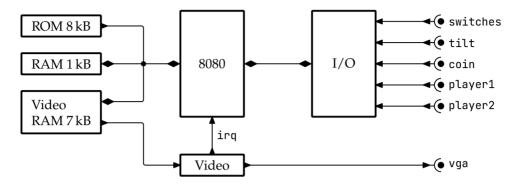

| 17                | -     | Invaders                                      | 431               |

|                   | 17.1  | 0 1                                           | 432               |

|                   | 17.2  | 0                                             | 433               |

|                   | 17.3  | Peripherals                                   | 434               |

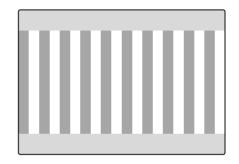

|                   | 17.4  | Video                                         | 436               |

|                   | 17.5  | Logic board                                   | 443               |

|                   | 17.6  | Simulation                                    |                   |

|                   | 17.7  | Summary                                       | 450               |

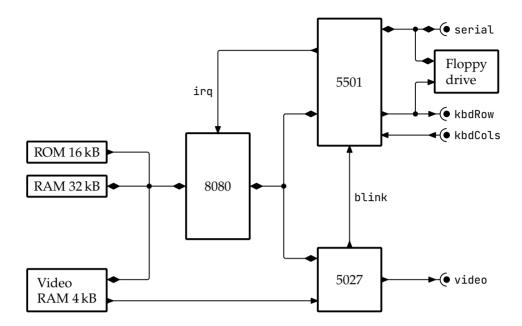

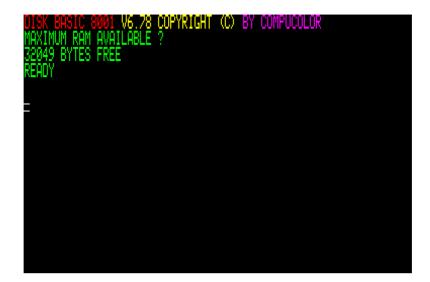

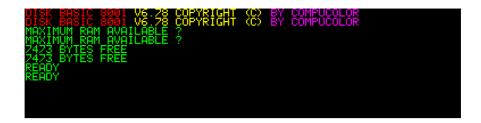

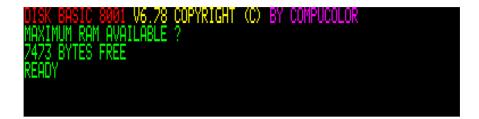

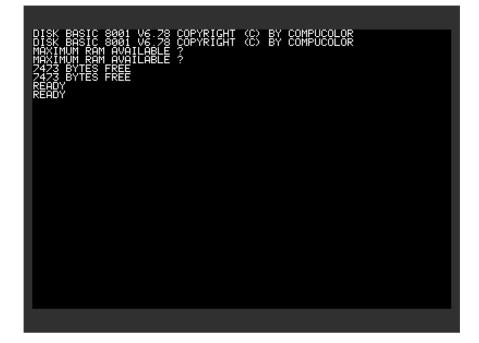

| 18                | Comp  | ucolor II                                     | 451               |

|                   | 18.1  | Design                                        | 451               |

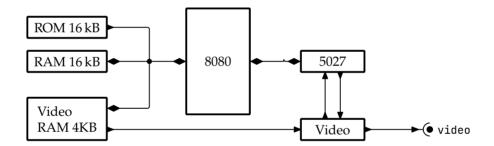

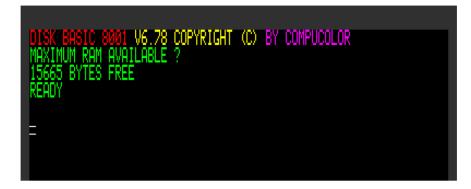

|                   | 18.2  | A Minimal Viable Compucolor II                | 454               |

|                   | 18.3  | Detailed rendering with SDL                   | 461               |

|                   | 18.4  | Video hardware                                | 467               |

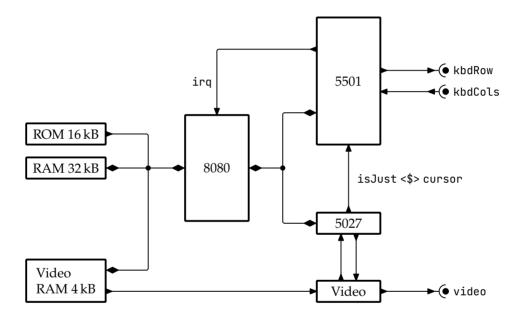

|                   | 18.5  | TMS 5501                                      | 484               |

|                   | 18.6  | Keyboard                                      | 499               |

| Parting words |                       |     |  |  |  |

|---------------|-----------------------|-----|--|--|--|

| 18.11         | Summary               | 526 |  |  |  |

| 18.10         | Our complete computer | 524 |  |  |  |

| 18.9          | Slowing down the CPU  | 521 |  |  |  |

| 18.8          | Cycle-count accuracy  | 517 |  |  |  |

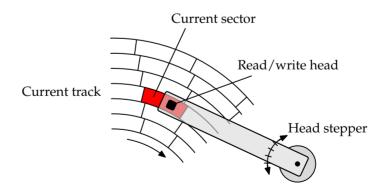

| 18.7          | Floppy drive          | 503 |  |  |  |

#### Index

#### Introduction

#### Preliminaries

In this book, we are going to assume at least intermediate level familiarity with Haskell. We will feel free to use many of GHC's general-purpose language extensions like DataKinds or TypeApplications, without introducing them. In fact, Clash, the main tool we will use throughout this book, turns on these (and many more) extensions by default. On the other hand, Template Haskell, being a more specialized tool that is not necessarily used by, the working Haskell programmer, will get its own introduction before using it in anger in chapter 14.

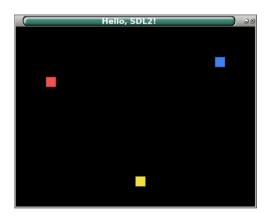

We take a similar approach to libraries: we will use *Containers*, the *Monad Transformer Library*, and small parts of *Lens*, assuming readers are either already familiar with them, or can look up the documentation as needed. Libraries for more niche domains, such as *Barbies* for easier handling of higher-kinded data types, *Terminal* for text IO, and *SDL2* for interactive, graphical applications, are described in detail alongside the parts of the book that use them.

#### Notation

In text, monospaced typeface denotes code fragments; the most common case is referring to Haskell types and functions by name, such as Bool or fmap. For the actual definitions that make up our programs, we will use code blocks like this:

Due to the limitations of paginated media, code blocks sometimes necessarily spread across page boundaries. Good code should tell a story, so in these situations, the cliffhangers get their own "to be continued" title card by drawing the code block's frame dashed, as in the following example:

predIdx :: (Eq a, Enum a, Bounded a) => a -> Maybe a

```

predIdx x | x == minBound = Nothing

| otherwise = Just $ pred x

```

Sometimes, we will build function or data type definitions piecewise over several blocks. In these cases, we will indicate where later parts are to be inserted, by including some of the previous code. Readers are very much encouraged to follow along by assembling the program from the parts and experimenting with the incomplete intermediate steps, not just looking at the final version.

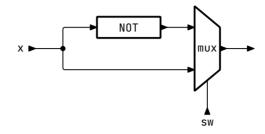

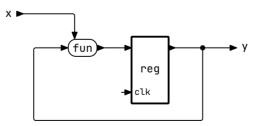

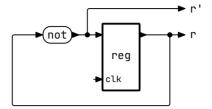

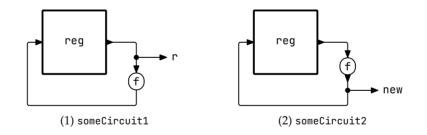

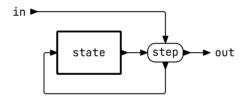

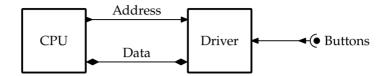

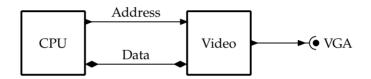

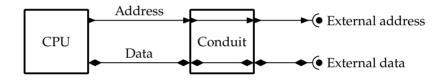

In illustrations, since we are creating hardware by writing code, the role of the schematic diagrams is just to provide overview. We will include more or less detail in these diagrams in different contexts. When we want to highlight the distinction between purely combinational circuits vs. stateful ones, we will enclose the pure parts in rounded shapes, like the not circuit in the following example:

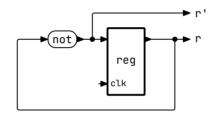

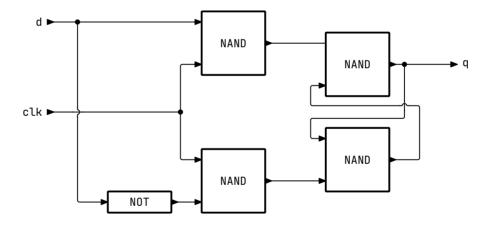

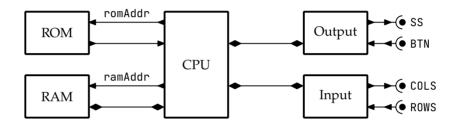

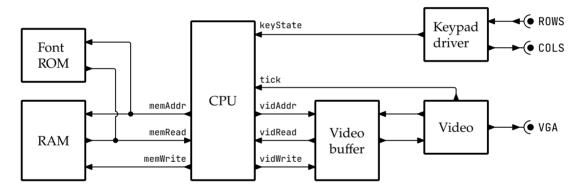

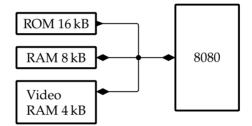

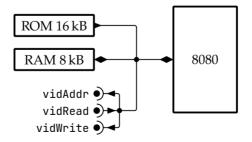

When the details of memory access are the focus of discussion, we will draw separate connections for address, read, and write lines. In other contexts, we will keep our diagrams easier to read by using a single connection, denoting the read-only, write-only, or read/write access by the direction of the connection:

(1) Detailed memory connections

#### Resources

The website of this book is at https://unsafePerform.IO/retroclash/ with links to repositories of the full source code of all programs appearing in the book.

#### Acknowledgements

I don't know if it takes a village to write a book, but a village certainly came together for this one.

Even before the idea of writing a book, I've been regularly bouncing my increasingly hare-brained schemes of describing hardware with all the abstractions afforded by Haskell with Marten Ågren, Nguyễn Hữu Hải, and Raphael Montelatici. Hải originally put the bug in my ear that I should tell not just them, but the whole world about these ideas.

Once I got to writing, Christiaan Baaij supported this endeavor from the get-go. The whole Clash development team and QBayLogic got busy to fix the various bugs I've uncovered on the way with very quick turnaround. Christiaan, Cosette Reczek, Andor Pénzes, Ellie Hermaszewska, Viktória Kiss, and Miëtek Bak provided invaluable feedback on the chapters as I wrote them. I have only myself to blame for any errors that might still have slipped through.

Károly Lőrentey helped me enter the world of typography beyond "whatever is default in LATEX", and Viktória had great ideas for how to turn some of the concepts in my head into illustrations. I am also indebted to TEX.stackexchange.com in their assistance in turning these ideas into reality.

• • •

But before any of that, there was my father, bringing first an Atari 2600 home, then a short while later, a Commodore 64. Followed by countless nights figuring out *Impossible Mission 2*, and countless days designing BASIC programs and drawing sprites of red balloons on graphing paper. He would have enjoyed — not the technical details — but certainly the *idea* of this book.

## Into the world of FPGAs

This book is about the intersection of FPGAs, retrocomputing, and Haskell; approaching the topic from the direction of Haskell. In other words, we expect readers to be familiar with traditional (software) programming in Haskell, and will concentrate on the hardware aspects. This chapter's goal is to introduce FPGAs, and to make our argument for picking retrocomputing as our topic.

#### 1.1 Computers everywhere

We are surrounded by computers. Smartphones are computers. Gaming consoles are computers. Smart TVs are computers, but so are "dumb" ones as well. Washing machines are computers. Bluetooth headphones are computers, as are non-Bluetooth noise canceling ones. *Computers are computers*. In fact, computers are surrounded by smaller computers in their peripherals: there's a computer in the keyboard, there's one in the mouse, and there's one in the network adapter.

If everything is a computer, does that make the term meaningless? No. What we mean by the word "computer" here is an artificial physical device designed to implement a finite approximation of a Turing machine. There are many proposed ways of building devices that perform computation: we can build a computer from water running through an elaborate network of pipes; we can synthesize organic molecules whose interaction corresponds to computation; there are even children's toys in which a ball falling through a lattice of pins and spindles can perform universal computation achieving Turing-completeness.

However, there is only one substrate of computation that sees real-world use: digital electronics. If we look at all these computers around us as physical artifacts, we see that they contain a bunch of functionality-specific parts (the drum of the washing machine, the speaker of the headphone, or the LCD of the TV) and one or more fiberglass epoxy boards (the *printed circuit boards* or *PCBs*) containing small plastic boxes and electric components (mostly resistors and capacitors), with copper traces running between the parts. To the naked eye, the epoxy boards look very similar across devices, even though the washing machine is a lot less capable a computer than a smartphone.

Amazingly, this similarity runs much deeper. Resistors are resistors, capacitors are capacitors, copper is copper, so the difference must be inside those small plastic boxes, right? If we zoom in on the inside of one of those boxes, we find a tiny silicon plane called an *integrated circuit* or *IC* for short. And if we zoom in much, much more, we will see that on these planes, all ICs are made up of a large number of components: a small portion is tiny versions of the resistors, capacitors, and other electric components we've seen earlier, and the rest are transistors.

Different chips have different sized transistors; the rapid advancement in computing performance since the first computers is in large part because of improvements in integrated circuit manufacturing. Newer transistors are smaller, use less energy, and so more of them can be packed into the same area. But functionally, all these transistors, large and small, are exactly the same: a tiny version of an electric switch where being short or open is itself also controlled electronically.

What this means is that the difference between the microcontroller in a toaster and the processor of a top-of-the-line supercomputer is only in how many of these transistors are connected to each other, and what the connections are. The key corollary is that we can build our own computer just by deciding on the connections.

#### 1.1.1 Digital electronics

As the saying goes, in theory, theory and practice are the same, but in practice, they are not. The above description of the insides of a computer is a gross simplification, glossing over a lot of the electrical components. However, we are in good company by making these simplifications: when we say that the computer is made of a network of transistors and nothing more, we are using the *digital abstraction*.

The idea of digital electronics is to pretend that every transistor lead and every pin visible to the outside world is always at one of only two voltage levels, referred to as "low" and "high" voltage. Of course, nature is messy, and it takes considerable electrical engineering effort to maintain this abstraction. In fact, for purely digital circuits, the role of everything else on the circuit board (resistors, capacitors, etc.) is to ensure that the digital abstraction isn't leaky.<sup>1</sup>

In this book, we will stay firmly inside the confines of the digital abstraction. When interfacing with the rest of the world, we will assume that the peripheral hardware contains sufficient circuitry to solve impedance mismatches, translate between voltage levels, and so on.

<sup>&</sup>lt;sup>1</sup>There are also circuits where the functionality is intrinsically tied to non-digital electronics, e.g. a radio receiver. Here, we regard those parts in the same way as we regard the heating coil of a toaster: a peripheral that interfaces with the digital parts, but isn't part of the "computer" proper.

#### 1.1 Computers everywhere

#### 1.1.2 Universality

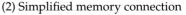

From two transistors, we can build a NAND gate: a two-input, one-output circuit where the output is the complement of the two input's conjunction (the name "NAND" stands for "NOT-AND"); in Haskell notation, we could write it as  $x y \rightarrow not (x \&\& y)$ . By using enough NAND gates, we can implement any function mapping *n* Boolean inputs to *m* outputs. This property of the NAND gate is called *universality*.<sup>2</sup> By way of example, the following circuit diagram implements a NOT gate from a single NAND gate; armed with NOT and NAND, we can directly implement all the usual binary Boolean functions, since e.g. x AND y = NOT (x NAND y) and x OR y = NAND (NOT x) (NOT y).

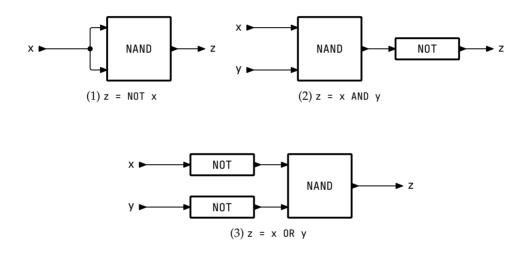

In most devices, however, the outputs are not purely a function of the inputs: there is also some *internal state*. By wiring together four NAND gates in a crossover configuration, we can create a so-called *latch*: a circuit with two inputs (*data* and *enable*) and one output where the output "remembers" what its data input was the last time the enable input was high:<sup>3</sup>

<sup>&</sup>lt;sup>2</sup>For any given concrete function, it is entirely possible that we can design a circuit that implements that function using fewer transistors than the one built from NAND gates. The point here is that via the NAND gate's universality, we can show that *any* function can be built just by wiring together transistors, without needing any other components.

<sup>&</sup>lt;sup>3</sup>More specifically, this configuration is called a *D latch*. Other latch types with slightly different behavior are also used in circuit design; for example, an *SR latch* also has two inputs, but the output "remembers" which of the two inputs was last seen high.

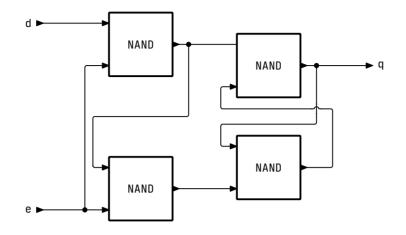

Adding one more NAND gate, we can build a *flip-flop*: a latch that is triggered not by a high enable input, but by the enable input (called the *clock* in this case) *changing* from low to high. As we will see in chapter 4, clocks are essential to compositional circuit design.

To summarize, it is possible to build this tower of abstractions where the higher levels correspond to the purely functional and the stateful parts of a given device's intended behavior, but at its foundation, everything is built up of the same basic element of the NAND gate.

#### 1.2 Field-programmable Gate Arrays

The rest of this book is about building even higher abstractions to make it manageable to design large circuits that implement complicated behavior. But once we have

#### 1.2 Field-programmable Gate Arrays

such a design, how are we going to turn that into physical hardware?

As we have seen, one solution would be to climb all the way down into the world of transistors, and wire them together. This is exactly what happens in traditional chip design: the output of the development work is the placement and connection of every single transistor, in a blueprint that is then shrunk down onto silicon wafers. The high-level design happens within the confines of the digital abstraction, but since the end result is a physical artifact, it will be subject to all laws of physics, not just the ones we'd like to apply: part of the design work is to address the electrical requirements of *maintaining* the digital abstraction. The cost of a full roundtrip from design to physical chip is enormous: depending on the details of the manufacturing process, it can cost millions of dollars. This is very different from the world of software, where a full from-scratch compilation of a program is essentially free.

The alternative is to develop using a so-called *field-programmable gate array*, or *FPGA* for short. As the name implies, an FPGA is a large number of logic gates where the connections between the gates can be set "in the field", i.e. after the manufacturing process. From the outside, an FPGA looks like any other fixed-layout chip, but internally, the connections between the gates are configured electronically from an uploaded schematic. Trying out a new design is as simple as recompiling the design into its low-level gate-by-gate representation, running a tool that creates a circuit layout confirming to the intended connections, and uploading this new layout. Functionally, it's like having our own chip factory!

The compromise in FPGAs is that the programmable interconnects are much more complicated than fixed traces: they use up some of our transistor budget. The consequence is that an FPGA is more expensive (per unit) and uses more power than a purpose-built chip. It is also not quite a standalone component: since the whole point is to keep the configuration dynamic, external support elements are needed to provide the programming at power-up.

These drawbacks are less relevant to us in this book:

- Unit cost: we are not interested in designing for manufacturing, but in creating one-off circuits. Furthermore, our designs are simple and small enough that they use a small number of components, fitting onto low-tier hobbyist FPGAs instead of the expensive, top-of-the-line, very fast, very large offerings.

- Power consumption: we will not design for embedded applications, and because we will be implementing old computers that were very slow compared to today, our designs will not need to run anywhere near the power/heat limits of today's FPGAs.

- Supporting circuitry: tying back to building one-offs, we will use pre-made development boards instead of designing our own purpose-built PCBs around

bare FPGA chips. These off-the-shelf development boards contain everything needed to make the FPGA work, freeing us up to care only about the circuit design inside the FPGA.

#### 1.2.1 From design to a network of NANDs

Suppose we design a circuit that has 16 inputs and 25 outputs: the inputs are grouped into two 8-bit numbers x and y, and the output consists of the bits of (complement x, complement y, x + y). The third component of the output, x + y, is 9 bits long, to account for the possibility of carry.

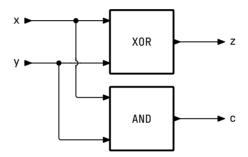

We have already seen how to use one NAND gate per bit for the complement. For the addition, we start with adding just two one-bit values: the so-called *half adder*:

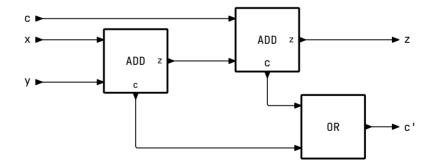

To extend this to multiple bits, we need a way to propagate the carry outputs from lower bits to higher ones. A *full adder* has an additional third input for the carry-in, i.e. the carry-out from the lower bit-pair:

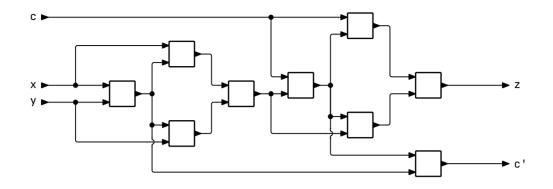

We can build circuits for AND, OR, and XOR using 2, 3 and 4 NANDs respectively. This gives us a total NAND count of 6 for the half-adder, and so 15 for the full adder. Alternatively, by breaking the abstractions, we can use just 9 NAND gates to implement the same functionality (in this diagram, every gate is a NAND gate, so we omit labels to save on space):

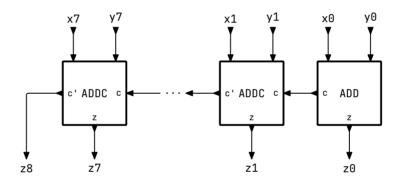

Regardless of which implementation we use for our full adder, we can then build the 8-bit adder by connecting 8 of our full adders in a so-called *ripple-carry configuration*:

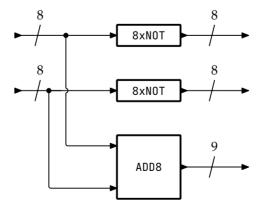

We are now ready to assemble our complete circuit, using the components defined above:

The slashes on the lines here emphasize the fact that each line actually corresponds to multiple (8 or 9) wires. Pretending that we have "wide" (multi-bit) lines (called *bus*es) is a very useful abstraction in avoiding clutter. In fact, it is so useful, that in the rest of this book we will use it all the time without using these bus marker slashes to distinguish them; one-bit lines will be thought of as degenerate buses that just happen to be one-bit wide.

What this final image tells us is that we can take  $8 \cdot 1 + 8 \cdot 1 + 8 \cdot 9 = 88$  NAND gates, connect them in the configuration that we see when all the abstract boxes are inlined, and the resulting 16-input 25-output circuit will implement our desired behavior.

#### 1.2.2 Lookup tables as basic elements

Since the complicated part of an FPGA is the electronically configurable routing between elements, and of course the more elements we have, the more routing is needed between them, it makes sense to reduce that complexity by using fewer, larger elements. This is why FPGAs are not called field-programmable *transistor* arrays: although everything is built from transistors, the basic unit of addressing is not a single transistor, but larger elements built from it. The idea is that for any circuit we would actually want to design, it will have a lot more structure than just a network of transistors.

Looking at our previous example, suppose we also have NOT gates as basic elements, still implemented with a single NAND gate internally. While this doesn't save on the total number of NAND gates, it does cut down on the number of junctions: in contrast to a NAND element that has three leads connected in a certain way to implement a NOT gate, a dedicated NOT element only has two leads. Thus, for the 16 NOT gates, the number of junctions goes down from  $16 \cdot 3 = 48$  to  $16 \cdot 2 = 32$ .

We can save a lot more junctions if we also have full adders as basic elements, since now we only need routing between 16+8 = 24 elements instead of the original 88.

In this hypothetical example, the reduction in routing was achieved by the design of the circuit matching the underlying FPGA's structure perfectly: the FPGA had NOT gates and full adders as basic elements, and our circuit trivially decomposed into complements and addition. But the whole point of an FPGA is to be versatile.

The answer to this seeming contradiction is to make the basic elements themselves configurable. On an FPGA, instead of using fixed-function gates like NOT or ADD, each basic element is a tiny piece of memory called a *lookup table* (*LUT* for short) that is initialized together with the inter-element connections. For example, if each element is a memory with 3 address bits and 2 data bits, we can put a  $3 \times 2$  lookup table into it. That is good for two NOT gates, or one full adder.

#### 1.2 Field-programmable Gate Arrays

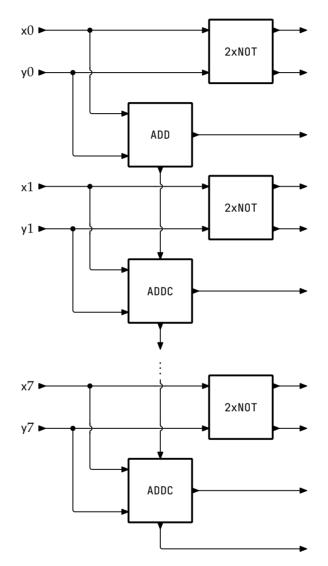

In the following diagram, the 2xNOT, ADD, and ADDC blocks all refer to  $3 \times 2$  LUTs loaded with the truth table of two parallel NOT gates, a half-adder, and a full adder, respectively. Unused inputs and outputs (such as the third input of a 2xNOT element) are omitted.

So now we can take just 8 + 8 = 16 elements to implement our circuit, without requiring the FPGA to be designed with prescience to our intended use case. On the other hand, we have now introduced additional complexity to the design process itself. Although our problem statement was "the bits are complemented", we now

need to group that into two-bit units just to get better resource utilization. Then a new FPGA model comes out with 3-output basic elements, and now we need to rework our design to take advantage of being able to put three NOT gates on one lookup table.

What happens in practice is that the details of lookup table dimensions and routing distances are hidden from the developer, and handled by vendor- and model-specific toolchains. We write our circuit in terms of one-bit NOT gates, and let the compiler (commonly called *synthesizer* in the FPGA context) figure out the nicest way to map that onto the elements available on our target FPGA.<sup>4</sup>

#### 1.2.3 FPGAs as hardware gadgets

Now that we have an idea of what goes on *inside* an FPGA, what is it actually, as a physical device? Although we include many simulators in this book, ultimately, the payoff is in synthesizing and uploading the designs into FPGAs. So what does that look like?

For development purposes, our best bet is to get an FPGA *development board* aimed at educational uses: a standalone hardware gadget that contains the FPGA; its support components such as flash ROM that will store its configuration between power cycles; some hardware peripherals like pushbuttons, toggle switches, LEDs, or seven-segment displays; connectors in standard format for further peripherals like USB for input devices or VGA for video output; a USB connector to upload the synthesis result from a computer; and some way of powering the board when not connected to a computer, usually in the form of a micro-USB socket or simple DC input.

Development boards are useful for us because they take care of all the electronic concerns that are outside the scope of this book. For example, lighting an LED on the board is as simple as setting the appropriate output pin's value to high, without having to worry about voltage levels and making sure the current won't be too large to fry the LED. They are also satisfyingly tactile: unlike a PC expansion card, we can hold the whole thing in our hands, disconnect it from the programming computer, and enjoy that it really is a standalone circuit that does everything by its own power.

#### 1.2.4 Toolchains

In the software development world, we are used to open source, standardized compiler toolchains. Unfortunately, this is not at all the case for FPGAs. Each FPGA

<sup>&</sup>lt;sup>4</sup>Just like in software, squeezing out the maximum performance sometimes requires reaching through abstractions and taking into account the specifics of the target device. One advantage of reproducing old computers is that in this book, we will not get even close to needing to do that.

#### 1.3 Retrocomputing

vendor provides its own synthesis toolchain, containing a ton of model-specific knowledge.

The normal way of interacting with the toolchain is by writing the circuit description in a *hardware description language* (commonly abbreviated as *HDL*). The two big players in this space are VHDL and Verilog: both have IEEE standards describing them. The VHDL or Verilog input is then processed by vendor-specific tools, mapping parts of the circuit to various elements of the given FPGA model, and then producing an opaque binary blob called a *bitfile*, which can be uploaded with an (again, vendor-specific) tool to the FPGA.

Since all intermediate representations are non-standard and proprietary, anything we want to do will have to go via HDL. We can think of the situation similar to how we can use any programming language to run in the browser, as long as it is JavaScript. If we want to use some other language, our program has to be translated to JavaScript. This translation can be simple and direct, with the output being in direct correspondence with the input (e.g. TypeScript); or it can be very involved, as in the case of GHCJS that compiles Haskell into JavaScript.

Due to this non-standard, highly vendor-specific nature of the development environments, in this book, we will not look beyond creating the HDL source (and we will not even write any HDL by hand), and will assume the reader has read up on the specifics in the documentation provided with their FPGA development boards.

#### 1.3 Retrocomputing

The motivating examples in this book all fall into one of two categories: simple circuits that demonstrate a single functionality, and complex, fully-worked-out systems based on old computers. "Old" can mean different things to different people; for us, it means the time period when computers just started entering the lives of everyday people: the late seventies arcade machines and home computers.

It would be a lie to say that this choice has nothing to do with the author's age and childhood. However, there are two objective benefits to studying old computers:

- CPUs and computers that were considered simple and cheap even in their own time were designed by very small teams, sometimes individuals. This makes it possible to understand them holistically.

- The performance gap between then and now is so large, that we can get something working without having to worry about doing everything the most efficient way. The goal of this book is not to train professional hardware designers, but to learn about quaint old computers and to write down what

we learn in code that is not only functionally correct, but also nicely readable and concise for humans.

None of the techniques explored in this book are specific to retrocomputing; however, there are certainly some modern areas we don't venture into. As an example, we never even consider pipelined CPU designs.

#### 1.4 Haskell meets Hardware

Since Verilog and VHDL, the two standardized hardware description languages, are the lingua franca of FPGA toolchains, if we want to use Haskell as a "better HDL", we need a way to meet the toolchains on their own turf. The two approaches to this are as an embedded DSL (e.g. Lava), or as a compilation target (e.g. Clash).

#### 1.4.1 Lava

In the Lava approach<sup>5</sup>, the role of Haskell is that of a macro language: the library provides types corresponding to circuit fragments, and combinators over these types, and the ambient Haskell language can be used in building abstractions for how these fragments are put together. Internally, signals are represented as data that describes their definitions; to create the HDL output, we write a Haskell program that uses the Lava entry point that traverses that description for the value representing our complete circuit design, and then when we *run* that program, it writes out a file containing Verilog or VHDL source.

Because the primitives exposed by Lava correspond directly to the primitives of the target HDL, it is easy to track provenance of the output. Error messages, or results from downstream testing tools, are straightforward to interpret in the context of the source code. Of course, this correspondence becomes less straightforward as the Haskell code that generates that final circuit value becomes more involved; but even then, since the HDL output is created by running our program, we can use Haskell-runtime debugging tools to do further tracking.

Pushing further, since we have a Turing-complete macro language with rich types in the form of Haskell, we can fully automate source code creation, for example by writing an interpreter from our own high-level description into Lava code. Since the interpreter runs before the output HDL is consumed, there is no limitation in the structures that can be generated, and no interpretation overhead in the resulting HDL.

On the flip side, Lava is a first-order language over primitive HDL types only. We can use arbitrary Haskell types to drive our macro code, but the result is com-

<sup>&</sup>lt;sup>5</sup>There has been several dialects of Lava since its original 1998 paper, resulting in a whole family of implementations. At the level of granularity in this chapter, they can all be regarded as the same.

#### 1.4 Haskell meets Hardware

pletely disconnected from these types. For example, there is no concept of defining algebraic datatypes, or pattern matching on them, in Lava. There is no way to lift functions on pure values to functions on signals, short of generating a small ROM containing the complete graph of the function as a lookup table.

#### 1.4.2 Clash

The Clash approach uses GHC as a compiler frontend, consuming its Core intermediate language, inlining definitions to dissolve recursion, and mapping the result to HDL constructs. In this model, we write straight Haskell code, and then *compile* it with Clash instead of GHC.

This results in the ability to use all features of Haskell in our circuit descriptions. Our circuits can be pure functions, or, if state is needed, we use the built-in Signal type constructor, which is an applicative functor, allowing pure Haskell function definitions to be lifted to the world of signals. Signals can contain arbitrary Haskell types: the Clash compiler applies supercompilation techniques to get rid of intermediate signals of non-representable contents. For example, in something this simple:

#### (&&) <\$> xs <\*> ys

the result of (&&) <\$> xs is of type Signal dom (Bool -> Bool), but we don't need to worry about time-varying functions, since the full term is a Signal dom Bool where the function is statically known to be the logical-AND function.

One drawback of this methodology is that some generalizations require quite involved type-level programming, compared to the Lava/DSL approach where ultimately, we're stitching together term-level HDL fragments. We will see quite early in this book that for most uses, lists have to be replaced by length-indexed vectors, to ensure they can be manipulated with circuits of statically known size. In chapter 14, we will also encounter a situation where Clash's supercompilation technique is simply not sophisticated enough to deal with certain recursively defined, but finite, circuits.

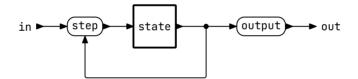

Nevertheless, this book puts its vote down firmly for Clash. One reason for this is that the intended audience is already familiar with Haskell and regards the type-level programming bits as fun and not scary at all. The second reason is that algebraic datatypes and pattern matching are simply too painful to live without. Starting at chapter 6, most of our circuit design will be based on translating input signals into a circuit-specific datatype, and consuming values of that datatype in the main state transition function.

## Hello, Clash!

In this chapter, we will write our first Clash program to connect some simple inputs to simple outputs. "Simple" here means that the digital signal connected to the FPGA's pins correspond directly to the peripheral's state. For example, a two-state switch connected to an I/O pin will pull that pin to either low or high depending on the position of the switch. Similarly, an LED is either on (lit up) or off (dark). Later, we will interface with more complicated peripherals that require coordination between multiple pins and/or through time.

Most FPGA development boards have some pushbuttons, switches and LEDs directly accessible from the FPGA; for those that don't, we can use a breadboard to connect these components as standalone parts to the so-called *general purpose I/O* (*GPIO*) pins of our board.

#### 2.1 Bit

Digital signal levels are represented by the Bit type in Clash. It has two values low and high, conversion functions boolToBit and bitToBool, and is an instance of standard Haskell typeclasses like Eq. Ord, Show, Bounded, and Enum. It is also an instance of Num as modulo-2 arithmetic, and Bits / FiniteBits in the straightforward way.

In this book, we will make an effort to keep Bool and Bit separate. For example, the signal level corresponding to a pushbutton connected to an I/O pin is a Bit, but whether the button is pushed or not is a Bool. Depending on how the pushbutton is wired in a given circuit, either high or low could be mapped to True. This can get tricky to track properly, so we will also define a newtype wrapper around Bit that tracks its polarity:

```

data Polarity = High | Low

newtype Active (p :: Polarity) = MkActive{ activeLevel :: Bit }

deriving (Show, Eq, Ord, Generic, NFDataX, BitPack)

```

active :: Bit -> Active p active = MkActive

This allows conversion of signal levels to logical Bool values, either by direct conversion (for Active High) or by taking the complement (for Active Low):

```

class IsActive p where

fromActive :: Active p -> Bool

toActive :: Bool -> Active p

instance IsActive High where

fromActive = bitToBool . activeLevel

toActive = MkActive . boolToBit

instance IsActive Low where

fromActive = bitToBool . complement . activeLevel

toActive = MkActive . complement . boolToBit

```

#### 2.2 Signal

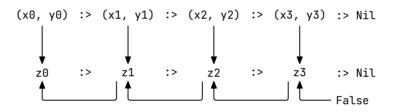

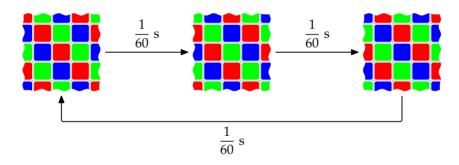

The Signal type represents time-varying values. Clash's model of time is *discrete* and *synchronous*: at every time step, all signals have some value and then in the next time step, all signals are updated. In Clash's simulator, signals are turned into streams (represented as infinite lists), with every element corresponding the the signal's value at a given timestep.

Signal is parameterized by the *clock domain* that a given signal belongs to. Clock domains are important because crossing over a signal from one domain to another requires special care. For example, imagine one domain operating at 100 MHz and another one at 1 MHz. If a signal in the faster domain changes value for a single (10 ns) cycle, and something is derived from it in the slower domain, what should happen during the whole 1  $\mu$ s cycle of that domain? There is no single, general, good answer to this. By tagging signals with their clock domains, Clash enforces that only signals in the same domain can be connected without explicitly taking care of these issues.

#### 2.3 Our first circuit

Armed with just Bit and Signal, we can now write our very first Clash program in just three lines:

```

-- This is the Clash equivalent of the Haskell Prelude

import Clash.Prelude

-- What `main` is for a Haskell program, `topEntity` is for Clash.

topEntity :: Signal System Bit -> Signal System Bit

topEntity = id

```

This defines a circuit which takes as input a one-bit signal, and returns it. Note the type of topEntity: it is a function from the Signal that represents the input to a Signal representing the output. Even though our circuits in this chapter are not going to be clocked (we'll learn about clocks in more detail in the next chapter), we still need to pick *some* clock domain, so we'll use System, which is defined for us in the Prelude.

If we connect a pushbutton to the input and an LED to the output, we get a simple electronic device that lights up an LED as long as the button is pressed. Or, depending on the wiring of the LED and the pushbutton, maybe it is going to light up the LED as long as the button is *not* pressed.

#### 2.3.1 Simulation

In its present form, we can't load this configuration onto a real FPGA board yet; we'll see shortly what else we need to add. But we can already play around with this circuit in the Clash simulator by loading it into the interpreter clashi, the Clash equivalent of ghci:

```

$ clashi Hello.hs

Clashi, version 1.4.2 (using clash-lib, version 1.4.2):

http://www.clash-lang.org/ :? for help

Ok, one module loaded.

```

As far as the Clash simulator is concerned, topEntity is a bona fide function, so we can apply it on an argument of type Signal System Bit:

```

> :t topEntity

topEntity :: Signal System Bit -> Signal System Bit

```

One way of getting our hands on a Signal System Bit value is to simulate a certain fixed sequence of events specified as a [Bit]. Let's see how our circuit would behave if we waited for two time steps, then pressed the button for one time step:

```

> let input1 = fromList [low, low, high]

> topEntity input1

0 0 1 *** Exception: X: finite list

```

Simulation failed after three clock cycles for the very simple reason that our input was only specified for three cycles. Let's fix that by appending infinitely repeating low values to our list:

The simulation will run indefinitely, until the heat death of the universe, or until we kill it with  $(C_{TRL} + (C))$ ; whichever happens first. So far, this author has always gone for the latter option.

Printing out the value of a signal timestep-by-timestep is useful for interactive examination, which is a fancy way of saying eyeballing. If we want to process it programmatically, it is usually a better idea to turn it into a list of values. This is what sample and sampleN do; the first one returns an infinite list, while the latter limits the simulation to n steps.

```

> L.take 20 $ sample $ topEntity input2

[0,0,1,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0]

> sampleN 10 $ topEntity input2

[0,0,1,0,0,0,0,0,0,0]

```

Both sample and sampleN are lazy, so they will work with our finite-length input1 as well:

```

> L.take 3 $ sampleN 10 $ topEntity input1

[0,0,1]

```

#### 2.3.2 Synthesis

Staring at signal traces in the simulator can be very useful, and in fact later on, we will do all our debugging in the simulator (and various different levels of simulation!) instead of on actual hardware. This is also how "real" ICs are developed, even more so than FPGA configurations, since round-tripping via a chip fab is both slow and expensive.

But we're here to put *fun* in *functional programming*! So let's put simulation behind us for a second, and try to get some LEDs on our FPGA dev board to light up.

We *could* take our program as-is, and tell Clash to compile it into some HDL we can then feed into our FPGA synthesis toolchain. However, because our input and output signals are not named, the resulting HDL will use the Clash-generated name c\$arg for our input port and the more reasonable result as the output port. By adding annotations to topEntity's type signature, the Template Haskell function makeTopEntity gives meaningful names to our I/O ports:

```

import Clash.Prelude

import Clash.Annotations.TH

topEntity

:: "BTN" ::: Signal System Bit

-> "LED" ::: Signal System Bit

topEntity = id

```

```

makeTopEntity 'topEntity

```

Note that the types of inputs and outputs are annotated with a type-level string denoting the port name to use. Clash supports currying for multi-input circuits; but the result type has to be a single type, since Haskell doesn't have multi-valued functions. Multiple outputs will have to be represented as a single output of some tuple type; more on that later. In later code listings, we will skip the makeTopEntity 'topEntity line.

We can use the meta-command :verilog in clashi to compile topEntity into  $\ensuremath{\mathsf{Verilog}}\xspace^1$

```

GHC: Parsing and optimising modules took: 0.603s

GHC: Loading external modules from interface files took: 0.000s

GHC: Parsing annotations took: 0.000s

Clash: Parsing and compiling primitives took 0.249s

GHC+Clash: Loading modules cumulatively took 1.301s

Clash: Compiling Main.topEntity

Clash: Normalization took 0.012s

Clash: Netlist generation took 0.000s

Clash: Total compilation took 1.315s

```

<sup>&</sup>lt;sup>1</sup>Why Verilog? Clash supports three mainstream Hardware Definition Languages: VHDL, Verilog, and SystemVerilog. SystemVerilog is not supported by older versions of the Xilinx ISE, needed to program popular FPGA dev boards such as the Papilio family, that are based on older Spartan-3 and Spartan-6 FPGAs; and Clash doesn't support VHDL for file-initialized ROM operations on Altera/Intel FPGAs. We'll be using Verilog throughout this book as the sweet spot.

This will create a file verilog/Main.topEntity/topEntity.v. How this is synthesized into FPGA configuration depends on what toolchain we use, which in turn is determined by the vendor of the FPGA chip we are targeting. One common trait among FPGA vendor tools is that they range from horribly painful to painfully horrible. In this book, interaction with the FPGA toolchain is restricted to a minimum by writing everything we can in Clash. However, mapping the port names such as BTN and LED to physical FPGA pins needs to be done outside Clash. Different toolchains, sometimes even from the same vendor, all have different formats for describing that mapping; usually, the easiest is to find this so-called *constraints file* on the dev board manufacturer's website and then tweak it to our needs.

Supposing we got over that hurdle, in the constraints file we can use the name BTN for one of the FPGA pins that is connected to a pushbutton on our development board. Alternatively, if we don't have a pushbutton, map BTN to a GPIO pin and connect a stand-alone pushbutton component to it via a breadboard. Similarly, map LED to a pin connected to an LED either directly, or via a breadboard. Then let the synthesis tool do its job to generate a *bitfile*, which is what can ultimately be uploaded to our FPGA.

#### 2.3.3 Running on real hardware

Finally, we have our bitfile and are ready to upload it! The details of uploading, again, are FPGA- and dev board-specific. Once it's on the board, we can press the button we chose in our constraint mapping, and observe the LED lighting up. Release the button, and the LED goes out as well. Reactivity!

Or maybe it is happening the other way round: if the pushbutton is wired such that it pulls the input low when pressed, but the LED is wired such that high turns it on, then it will go out when the button is held. The next chapter will show that Signal is an applicative functor, so we can use fmap complement to flip the input Bit.

Either way, this is not quite *blinkenlights* yet: all the *blinken* is still missing! Blinking requires *state*, which we will explore after the next chapter.

#### Exercises:

Try out what happens if we change topEntity's type to be Signal System Bool -> Signal System Bool. Does its behavior change? Does its intended meaning?

#### 2.4 Summary